新書推薦:

《

天命无常:五代十国 优酷人文·“梅毅说中国史”系列(全三册)

》

售價:HK$

151.8

《

武王墩:亲历2020—2024楚王墓发掘

》

售價:HK$

96.8

《

异化

》

售價:HK$

94.6

《

你的脆弱很正常

》

售價:HK$

60.0

《

鸟墙——康奈尔鸟类学实验室巨幅壁画诞生记

》

售價:HK$

195.8

《

政治人--政治的社会基础(东方编译所译丛)

》

售價:HK$

129.8

《

大国崛起战略论:地理与世界霸权+海权论+陆权论+空权论+战争论(全译足本无任何删节-同人阁)

》

售價:HK$

282.5

《

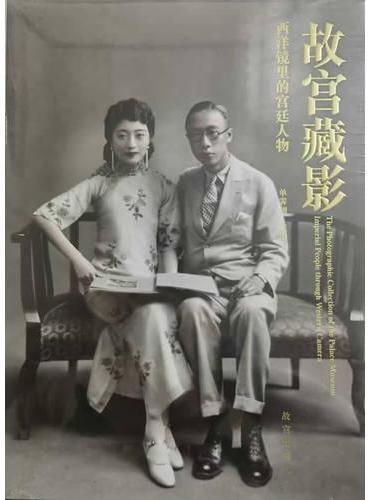

故宫藏影—西洋镜里的宫廷人物

》

售價:HK$

396.0

|

| 內容簡介: |

SystemVerilog是21世纪电子设计师必须掌握的最重要的语言之一,因为它是设计/验证现代复杂电子系统核心芯片的至关重要的手段。本书讲授用SystemVerilog语言设计/验证数字系统的基本概念和具体方法。在介绍基本语法的基础上,阐述了如何使用RTL级的SystemVerilog构成可综合的数字电路/组件/系统,以及如何使用行为级的SystemVerilog搭建测试平台对设计进行验证。

本书针对的读者群是电子、自动化和计算机工程专业的本科生与研究生,本书也适合已经掌握Verilog和VHDL硬件描述语言的工程师自学新一代的数字系统设计/验证语言。

|

| 目錄:

|

第1章 序言

1.1 现代数字设计

1.2 使用硬件描述语言进行设计

1.2.1 设计自动化

1.2.2 什么是SystemVerilog

1.2.3 什么是VHDL

1.2.4 仿真

1.2.5 综合

1.2.6 可重用性

1.2.7 验证

1.2.8 设计流程

1.3 CMOS技术

1.3.1 逻辑门

1.3.2 ASIC专用集成电路和FPGA现场可编程门阵列

1.4 可编程逻辑

1.5 电气属性

1.5.1 噪声容限

1.5.2 扇出

总结

参考资料

练习题

第2章 组合逻辑设计

2.1 布尔代数

2.1.1 值

2.1.2 操作符

2.1.3 逻辑门的真值表

2.1.4 布尔代数的定律

2.1.5德摩根定理

2.1.6 香农扩展定理

2.2 逻辑门

2.3 组合逻辑设计

2.3.1 逻辑最小化

2.3.2 卡诺图

2.4 时序

2.5 数字码

2.5.1 整数

2.5.2 定点数

2.5.3 浮点数

2.5.4文字数字字符

2.5.5 格雷码

2.5.6奇偶校验位

总结

参考资料

练习题

第3章 使用SystemVerilog门模型描述的组合逻辑

3.1 模块和文件

3.2 标识符、空格和注释

3.3 基本门模型

3.4 简单的网表

3.5 逻辑值

3.6 连续赋值语句

3.6.1 SystemVerilog操作符

3.7 延迟

3.8 参数

3.9 测试平台

总结

参考资料

练习题

第4章 组合逻辑构件

4.1 多路选择器

4.1.1 2选1多路选择器

4.1.2 4选1多路器

4.2 译码器

4.2.1 2到4译码器

4.2.2参数化的译码器

4.2.3 七段译码器

4.3优先编码器

4.3.1 无关项和唯一性问题

4.4 加法器

4.4.1 功能模型

4.4.2 逐位进位加法器

4.4.3 任务

4.5奇偶校验器

4.6 三态缓冲器

4.6.1 多值逻辑

4.7 组合逻辑块的测试平台

总结

参考资料

练习题

第5章 时序逻辑块的SystemVerilog模型

第6章 同步时序设计

第7章 复杂时序系统的设计

第8章 测试平台的编写

第9章 SystemVerilong的仿真

第10章 SystemVerilong的综合

第11章 数字系统的测试

第12章 可测试性设计

第13章 异步时序电路设计

第14章 与模拟电路的接口

附录A SystemVerilog与Verilog的关系

部分练习题的参考答案

参考文献

|

|